The main difference between Verilog and SystemVerilog is that Verilog is a Hardware Description Language, while SystemVerilog is a Hardware Description and Hardware Verification Language based on Verilog.

Hardware Description Language (HDL) is a computer language that is used to describe the structure and behaviour of electronic circuits. Hardware Verification Language is a programming language that is used to verify the electronic circuits written in a Hardware Description Language. Verilog is an HDL while SystemVerilog is an HDL as well as HVL. Overall, SystemVerilog is a superset of Verilog.

Key Areas Covered

Systemverilog New

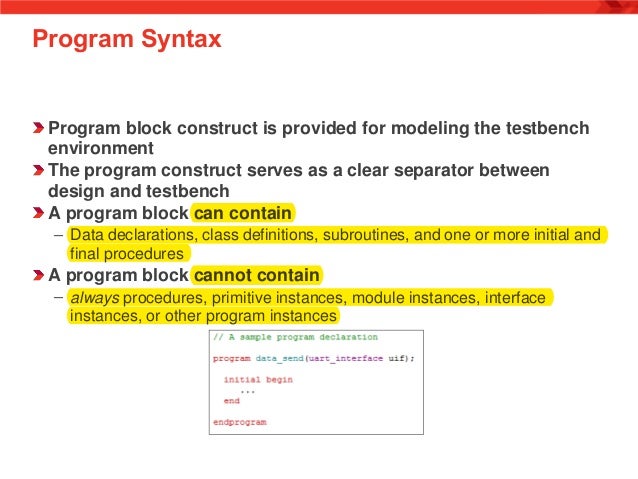

Module latch (output logic 31:0 y, input 31:0 a, input enable); always @(a iff enable 1) y block that is used to model combinational logic, forgetting an else leads to an unintended latch. To avoid this mistake, SystemVerilog adds specialized alwayscomb and alwayslatch. Program Block module in verilog is used for describing hardware, it can contain, always, intial and assign statments. To have clear sepration between testbench and design, SystemVerilog introduces program, which contains full enviroment for testbench. A Program serves following purpose. Online course in SystemVerilog for Functional Verification is a 12 weeks course structured to enable engineers develop their skills in full breadth of systemverilog features. VT-SVO course covers all aspects of functional verification including constrained random verification, assertion based verification and coverage driven verification. In the article, Blocking And Non-blocking in Verilog, we will discuss the topics of Verilog blocking and non-blocking. Blocking And Non-blocking In Verilog: The execution of the blocking statements will be in series. This blocking statement will block the next statement until the present statement executes successfully. Verilog Blocking and Non-blocking. Verilog supports blocking and non-blocking assignments statements within the always block with their different behaviors. The blocking assignment is similar to software assignment statements found in most popular programming languages.

1. What is Verilog

– Definition, Functionality

2. What is SystemVerilog

– Definition, Functionality

3. Difference Between Verilog and SystemVerilog

– Comparison of Key Differences

Key Terms

HDL, OOP, Verilog, SystemVerilog

What is Verilog

Verilog is a hardware description language. It also helps to verify analogue circuits and mixed-signal circuits and to design genetic circuits. In 2009, Verilog was combined with SystemVerilog standard. Therefore, Verilog is currently a part of SystemVerilog.

The main data types of Verilog are Wire and Reg. Wire denotes physical wire in a circuit that connects gates or modules. Reg holds value from one procedural assignment to the next.

Other frequently used keywords are as follows.

Input – Declares the input port of a task or module.

Output – Declares the output port of a task or module.

Inout – Declares bidirectional port of a task or module.

Verilog supports different levels of abstraction. Behavior level describes the concurrent algorithms. Register Transfer Level (RTL) explains the characteristics of a circuit by operations and the transfer of data among registers. Furthermore, Gate Level defines the logical links and their timing properties.

What is SystemVerilog

SystemVerilog is a hardware description and hardware verification language based on Verilog with additional features. It helps to model, design, simulate, test and implement electronic systems. Furthermore, SystemVerilog is mainly used in the semiconductor and electronic design industry.

Two data types specified in SystemVerilog are static and automatic. The programmer creates static variables at the beginning of executing the program. And, this value remains the same during the entire program’s lifespan. Also, this value can change when it is assigned a new value during the execution. Moreover, automatic variables are created at the moment the program execution comes to the scope of the variable.

SystemVerilog consists of three new procedural blocks. These help to model hardware. The always_comb helps to model combinational logic; always_ff is for flipflops whereas always_latch is for latches. An HDL compiler or a verification program ensures that only the required type of behaviour occurs. Moreover, SystemVerilog contains interfaces that help to reduce the redundancy of port-name declarations between connected modules.

Another important use of SystemVerilog is that it supports Object Oriented Programming. These classes support single inheritance model. However, a programmer can implement multiple inheritances using interfaces. He can also implement concepts such as polymorphism similar to C++. The local and protected keywords help to accomplish concepts such as encapsulation. By default, the class properties are public. Furthermore, SystemVerilog provides an automatic garbage collector.

Difference Between Verilog and SystemVerilog

Definition

Verilog is a Hardware Description Language (HDL) that helps to model electronic systems. In contrast, SystemVerilog is a Hardware Description, and as well as, a Hardware Verification Language used to model, design, simulate, test and implement electronic systems. Hence, this is the main difference between Verilog and SystemVerilog.

Paradigm

Also, another important difference between Verilog and SystemVerilog is that Verilog supports structured paradigm whereas SystemVerilog supports structured and object-oriented paradigms.

IEEE

Verilog is standardized as IEEE 1364 while SystemVerilog is standardized as IEEE 1800.

File extension

Systemverilog Spec

Moreover, Verilog has the file extension .v or .vh whereas SystemVerilog has the file extension .sv and .svh.

Influenced By

Furthermore, one other difference between Verilog and SystemVerilog is that the former is influenced by C and Fortran while the latter is influenced by Verilog, VHDL and C++.

Data types

Verilog supports Wire and Reg data types while SystemVerilog supports various data types such as enum, struct, union, class and string. Thus, this is also a difference between Verilog and SystemVerilog.

Procedural Blocks

Besides, Verilog has a single always block to implement combinational and sequential logic while SystemVerilog has always_comb, always_ff and always_latch procedural blocks.

Construction

While Verilog is based on a hierarchy of modules, SystemVerilog is based on classes.

Testbench

Verilog Vs Systemverilog

Additionally, Verilog uses module level testbench while SystemVerilog uses class-based testbench.

Conclusion

The main difference between Verilog and SystemVerilog is that Verilog is a Hardware Description Language, while SystemVerilog is a Hardware Description and Hardware Verification Language based on Verilog. In brief, SystemVerilog is an enhanced version of Verilog with additional features.

References:

1.“Verilog.” Wikipedia, Wikimedia Foundation, 3 Apr. 2019, Available here.

2.“SystemVerilog.” Wikipedia, Wikimedia Foundation, 10 May 2019, Available here.

3.Tala, Deepak Kumar. Introduction, 1 Feb. 1970, Available here.

Image Courtesy:

For Loop In Systemverilog

1.”The GTKWave window” By Screenshot made by ReAl. – Screenshot of free software (Public Domain) via Commons Wikimedia